#### PROPRIETARY RIGHTS STATEMENT

THIS DOCUMENT CONTAINS INFORMATION, WHICH IS PROPRIETARY TO THE CRYSTAL CONSORTIUM. NEITHER THIS DOCUMENT NOR THE INFORMATION CONTAINED HEREIN SHALL BE USED, DUPLICATED OR COMMUNICATED BY ANY MEANS TO ANY THIRD PARTY, IN WHOLE OR IN PARTS, EXCEPT WITH THE PRIOR WRITTEN CONSENT OF THE CESAR CONSORTIUM THIS RESTRICTION LEGEND SHALL NOT BE ALTERED OR OBLITERATED ON OR FROM THIS DOCUMENT. THE RESEARCH LEADING TO THESE RESULTS HAS RECEIVED FUNDING FROM THE EUROPEAN UNION'S SEVENTH FRAMEWORK PROGRAM (FP7/2007-2013) FOR CRYSTAL – CRITICAL SYSTEM ENGINEERING ACCELERATION JOINT UNDERTAKING UNDER GRANT AGREEMENT N° 332830 AND FROM SPECIFIC NATIONAL PROGRAMS AND / OR FUNDING AUTHORITIES.

## CRitical SYSTem Engineering AcceLeration

# UC 4.5 Software centric scalable safety critical medical display platform Tool and methodology report D405.010

## **DOCUMENT INFORMATION**

| Project             | CRYSTAL                     |

|---------------------|-----------------------------|

| Grant Agreement No. | ARTEMIS-2012-1-332830       |

| Deliverable Title   | Tool and methodology report |

| Deliverable No.     | D405.010                    |

| Dissemination Level | СО                          |

| Confidentiality     | R                           |

| Document Version    | V1.00                       |

| Date                | 2014-04-30                  |

| Contact             | Dominique Segers            |

| Organization        | Barco                       |

| Phone               | +32 56 233017               |

| E-Mail              | dominique.segers@barco.com  |

## **AUTHORS TABLE**

| Name                          | Company | E-Mail                           |

|-------------------------------|---------|----------------------------------|

| Dominique Segers              | Barco   | Dominique.Segers@barco.com       |

| Kurt Pattyn                   | Barco   | Kurt.Pattyn@barco.com            |

| Frederik Toune                | Barco   | Frederik.Toune@barco.com         |

| Reginald Swaenepoel           | Barco   | Reginald.Swaenepoel@barco.com    |

| Stephane Deltour              | Barco   | Stephane.Deltour@barco.com       |

| Bart Diricx                   | Barco   | Bart.Diricx@barco.com            |

| Ronny Van Belle               | Barco   | Ronny.Vanbelle@barco.com         |

| Adriaan Coosemans             | Barco   | Adriaan.Coosemans@barco.com      |

| Arjen van de Wetering         | IBM     | Arjen.van.de.Wetering@nl.ibm.com |

| Sytze S.H. Kalisvaart         | TNO     | Sytze.Kalisvaart@tno.nl          |

| Bardo B.J.H. Bakker           | TNO     | Bardo.Bakker@tno.nl              |

| Martijn M.H.P. van den Heuvel | TU/e    | m.m.h.p.v.d.heuvel@tue.nl        |

|                               |         |                                  |

## CHANGE HISTORY

| Version | Date        | Reason for Change                                    | Pages<br>Affected |

|---------|-------------|------------------------------------------------------|-------------------|

| 0.01    | 31 Mar 2014 | Initial version                                      | All               |

| 0.02    | 08 Apr 2014 | General update                                       | All               |

| 0.03    | 14 Apr 2014 | Update Engineering Methods for New SW Design Process | All               |

| 0.04    | 16 Apr 2014 | Final Update FUN100 Platform                         | All               |

| 0.05    | 21 Apr 2014 | Update of general structure                          | All               |

| 0.06    | 28 Apr 2014 | Update after review 1                                | All               |

| 1.00    | 29 Apr 2014 | Update after review 2                                | All               |

|         |             |                                                      |                   |

## CONTENT

| [ | D405.0         | 010                                                                    |                      | I       |

|---|----------------|------------------------------------------------------------------------|----------------------|---------|

| 1 | INTF           | RODUCTION                                                              |                      | 6       |

|   | 1.1            | ROLE OF DELIVERABLE                                                    |                      |         |

|   |                | RELATIONSHIP TO OTHER CRYSTAL DOCUMEN                                  |                      |         |

|   | 1.3            | STRUCTURE OF THIS DOCUMENT                                             |                      | 6       |

| 2 | USE            | CASE PROCESS DESCRIPTION                                               |                      | 7       |

| 3 | DET            | AILED DESCRIPTION OF DESIRED DESIG                                     | N PROCESS            | 8       |

| ( | 3.1            | HIGH LEVEL OVERVIEW OF THE DESIRED DESIGN                              | PROCESS              |         |

| : | 3.2            | DETAILED ACTIVITY DESCRIPTION                                          |                      |         |

|   | 3.2.1          |                                                                        |                      |         |

|   | 3.2.2          |                                                                        |                      |         |

|   | 3.2.3          |                                                                        |                      |         |

|   | 3.2.4          | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                |                      |         |

|   |                | CONCLUSION                                                             |                      |         |

| 4 |                | NTIFICATION OF ENGINEERING METHOD                                      |                      |         |

|   |                | BARCO ROADMAP AND THE SELECTED CRYSTA                                  |                      |         |

| 4 |                | TRACK 1: NEW SOFTWARE DESIGN PROCESS                                   |                      |         |

|   | 4.1.1          |                                                                        |                      |         |

|   | 4.1.2<br>4.1.3 | <b>3</b> • • <b>3</b> • • • • • • • • • • • • • • • • • • •            |                      |         |

|   | 4.1.3          | <b>3</b> • • <b>3</b> • • • • • • • • • • • • • • • • • • •            |                      |         |

|   | 4.1.5          |                                                                        |                      |         |

|   | 4.1.6          |                                                                        | 5                    |         |

| 4 |                | TRACK 2: FUN100 DESIGN PROCESS                                         |                      |         |

|   | 4.2.1          |                                                                        |                      |         |

|   | 4.2.2          | 2 IEC-62304 compliant Test Framework for                               | r FUN100             |         |

|   | 4.2.3          |                                                                        |                      |         |

|   | 4.2.4          |                                                                        | g for FUN100         |         |

|   | 4.2.5          |                                                                        |                      |         |

|   | 4.2.6          |                                                                        |                      |         |

| 4 |                | TRACK 3: FLEXIBLE SW CENTRIC DISPLAY DESI                              |                      |         |

|   | 4.3.1<br>4.3.2 |                                                                        |                      |         |

|   | 4.3.2          | <b>J</b>                                                               |                      |         |

|   | 4.3.4          | <b>a</b>                                                               |                      |         |

|   | 4.3.5          |                                                                        |                      |         |

| 4 | 4.4            | CONCLUSION: TECHNICAL CORE REQUIREMENT                                 | 5                    |         |

| 5 | SYS            | TEM ENGINEERING ENVIRONMENT                                            |                      | 44      |

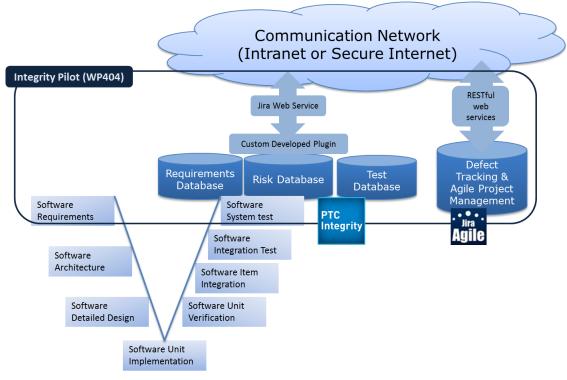

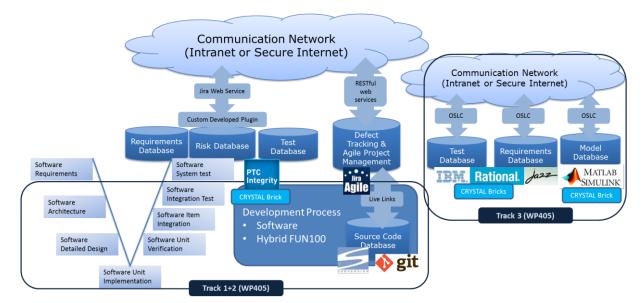

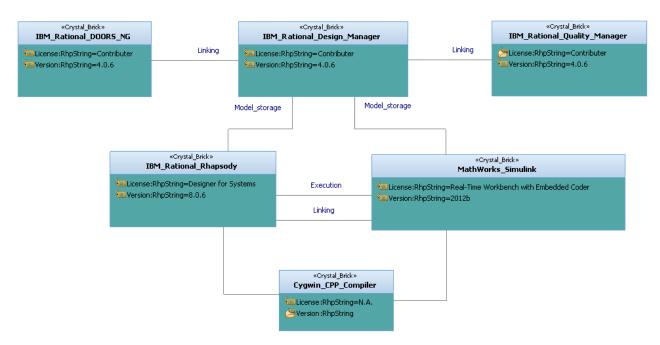

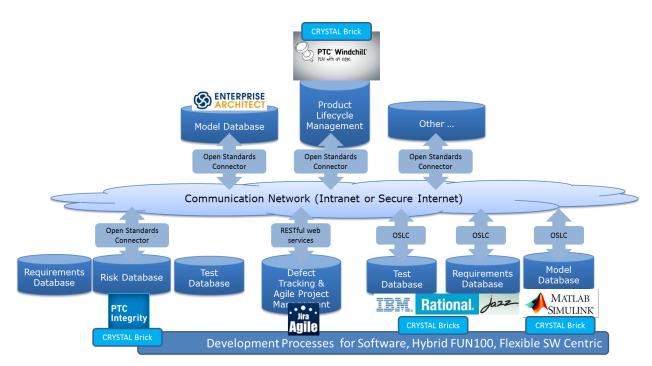

| Į | 5.0            | INTRODUCTION: HIGH LEVEL OVERVIEW OF THE                               | VP404-405 SEE AT M12 |         |

| ł |                | TRACK 1: SEE FOR THE NEW SOFTWARE DESIG                                |                      |         |

| ł |                | TRACK 2: SEE FOR FUN100 AT M12                                         |                      |         |

|   | 5.2.1          |                                                                        |                      |         |

|   | 5.2.2          |                                                                        |                      |         |

|   |                | TRACK 3: SEE FOR FLEXIBLE SW CENTRIC DIS<br>CONCLUSION: ENVISIONED SEE |                      |         |

| 6 |                | LEMENTED ENGINEERING METHODS                                           |                      |         |

|   | ersion         | Confidentiality Level                                                  | Date                 | Page    |

|   | 01.00          | R                                                                      | 2014-04-30           | 4 of 75 |

| v | 01.00          | IN IN                                                                  | 2017-04-00           | 40173   |

|   | 6.1 Tr  | ACK 1: NEW SOFTWARE DESIGN PROCESS                                         |    |

|---|---------|----------------------------------------------------------------------------|----|

|   | 6.1.1   | Engineering Method: Requirements Traceability                              |    |

|   | 6.1.2   | Engineering Method: Key Quality Metrics                                    |    |

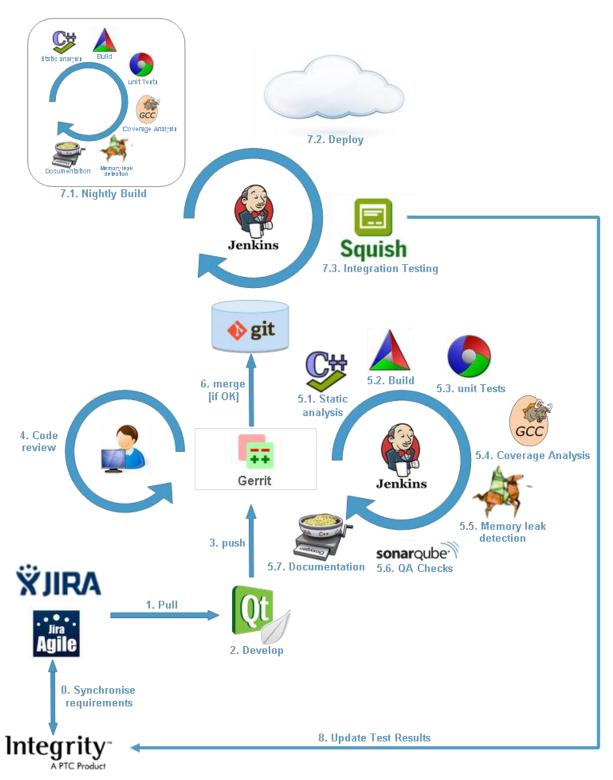

|   | 6.1.3   | Engineering Methods: Iterative Development & Process Automation            |    |

|   | 6.2 Tr  | ACK 2: FUN100 DESIGN PROCESS                                               |    |

|   | 6.2.1   | Engineering Method: Software Unit Testing                                  |    |

|   | 6.2.2   | Engineering Method: Component Testing                                      |    |

|   | 6.2.3   | Engineering Method: Architectural Design for FUN100                        | 60 |

|   | 6.2.4   | Engineering Method: Software Engineering for FUN100                        |    |

|   | 6.3 Tr  | ACK 3: FLEXIBLE SW CENTRIC DISPLAY PLATFORM DESIGN PROCESS                 | 67 |

|   | 6.3.1   | Engineering Method: Functional Modeling                                    |    |

|   | 6.3.2   | Engineering Method: Performance Simulation                                 | 67 |

|   | 6.3.3   | Engineering Method: Combining Functional Modeling & Performance Simulation | 69 |

| 7 | DEMO    | NSTRATOR DESCRIPTION                                                       | 71 |

| 8 | CONCL   | LUSIONS AND WAY FORWARD                                                    | 73 |

|   | 8.1 Co  | NCLUSION                                                                   | 73 |

|   | 8.2 INT | EROPERABILITY ISSUES                                                       | 73 |

|   | 8.3 WA  | AY FORWARD                                                                 | 74 |

| 9 | TERMS   | S, ABBREVIATIONS AND DEFINITIONS                                           | 75 |

# 1 Introduction

## 1.1 Role of deliverable

This document has the following major purposes:

- Define of the overall use case, including a detailed description of the underlying development processes and the set of involved process activities and engineering methods.

- Provide input to WP601 (IOS Development) required to derive specific IOS-related requirements.

- Provide input to WP602 (Platform Builder) required to derive adequate meta models

- Establish the technology baseline with respect to the use-case, and the expected progress beyond (existing functionalities vs. functionalities that are expected to be developed in CRYSTAL).

## **1.2 Relationship to other CRYSTAL Documents**

This version is the first iteration of this deliverable giving an overview of the desired use case process and the selected engineering methods.

During the course of the CRYSTAL project a total of 3 iterations are foreseen.

New engineering methods and corresponding tool requirements will be added with the following iterations.

## **1.3 Structure of this document**

The CRYSTAL activities focus on setting up the desired process for the Barco software centric scalable safety critical medical display platform. Chapter 2 provides an overview of the general Barco use case, for this section we refer to the CRYSTAL Deliverable D\_404\_010. Chapter 3 describes the envisioned use case design process. Chapter 4 describes all identified CRYSTAL activities and the link with the Barco roadmap. Chapter gives an overview of the SEE at 12. Chapter 6 show the first implementation results in the new design processes. The selected demonstrator description is given in chapter 7. Finally chapter 9 is summarizing the conclusions for year 1 and looks ahead to the future work for this project.

# 2 Use Case Process Description

For more details about the Barco Use Case Process Description we would like to refer to section 2 of the Use Case Process' of CRYSTAL Deliverable D\_404\_010.

# **3 Detailed Description of Desired Design Process**

Section 3 is describing a more detailed description of the desired design process for the Flexible SW Centric display platform.

## 3.1 High level overview of the Desired Design Process

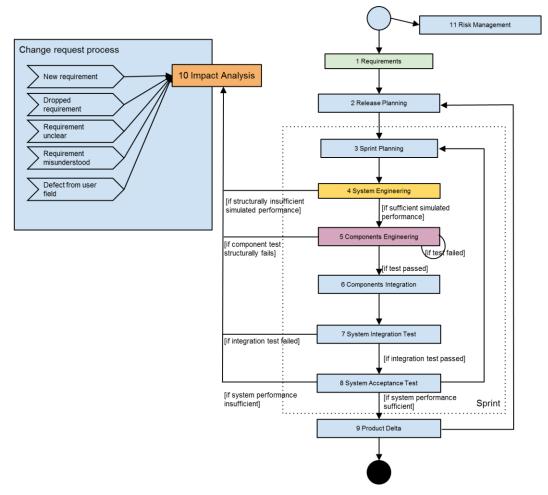

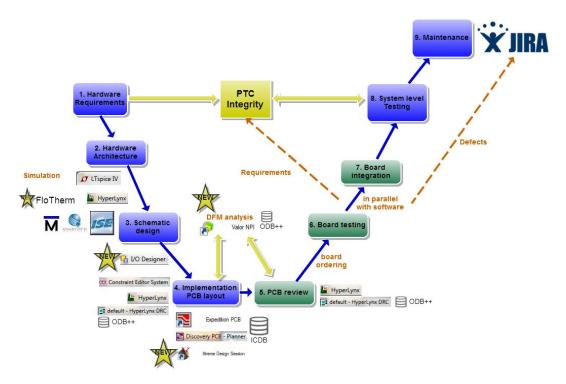

Figure 3-1 describes the desired development process used for a software-centric and cost-effective replacement of the image pipeline. It is represented as series of activities ('activity diagram') that are executed to deliver the product.

Figure 3-2 shows the legend for all symbols that are used to describe this process. The activities are represented by a rectangle. The start of our development process is indicated by an open circle. The process ends with a completed product and is represented by a solid black circle.

The process is repetitive and uses an agile approach to come to the final product in series of refinement steps, the dotted box surrounding step 3 till 8 indicates one sprint cycle in the agile process.

Step 10, the impact analysis, is the activity in which the appropriate action is decided for all setbacks (arrows going to the left and up) or unexpected events (event blocks at left). At the appropriate level of the development team (e.g. software team for software component changes, system architect for changes in functions or decomposition), the implications of the changes are discussed, the consequences for other components are analysed and the proposed actions on the various levels of the development process are determined. This could be for example adding one requirement or changing a set of related requirements; could imply a change of architecture or could imply a reallocation of functions between two GPUs.

Figure 3-1: Software Display System Process.

Figure 3-2: Process Activities Legend.

Short description of the activities:

### 1. Requirements

During this activity the Stakeholder Requirements are captured, maintained and managed. <u>Input artefacts:</u> Market analysis, stakeholder interviews, legal standards. <u>Output artefacts:</u> Prioritized Stakeholder Requirements, Product Backlog.

## 2. Release Planning

Based on the Stakeholder Requirements the product development is planned with respect to releases and their features.

Input artefacts: Prioritized Stakeholder Requirements, Product Backlog.

<u>Output artefacts:</u> Business Case, Release Definition, traceability from Releases to Stakeholder Requirements.

## 3. Sprint Planning

A Work Breakdown Structure is created for the product release of which the development is started.

Input artefacts: Release Definition, Product Backlog.

Output artefacts: Work Breakdown Structure, Sprint Backlog.

## 4. System Engineering

During this activity the System Requirements are created and an executable System Architecture is defined and verified by simulation. The System Architecture describes the complete system with all the engineering disciplines such as mechanical, electrical and software.

## Input artefacts: Stakeholder Requirements

<u>Output artefacts:</u> System Requirements, Executable System Architecture (System Use Cases, Architectural Decomposition, Component Descriptions, Executable Functional Models), System Requirements to Stakeholder Requirements traceability, System Use Case to System Requirements traceability, Architecture to System Requirements traceability, Trade-off Analysis Report, System Performance Analysis Report.

### 5. Components Engineering

The architectural components that are defined during System Engineering are handed over to the engineering disciplines where they will be defined, designed, created and tested.

Input artefacts: System Requirements, Executable System Architecture, Component Description.

<u>Output artefacts:</u> Component Requirements, Component Design, Realized Components, traceability from Requirements to System Requirements, traceability from Component Design to Component Requirements.

### 6. System Integration

The components that make up the system are integrated, thus assembling a part of or the complete system.

Input artefacts: To be decided.

Output artefacts: To be decided.

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 10 of 75 |

## 7. System Integration Test

The system is tested with respect to the system requirements that are created during Systems Engineering.

Input artefacts: To be decided.

Output artefacts: To be decided.

## 8. System Acceptance Test

The system is validated with respect to the stakeholder requirements that are captured during the Requirements activity.

Input artefacts: To be decided.

Output artefacts: To be decided.

## 9. Product Delta

To be decided. <u>Input artefacts:</u> To be decided. <u>Output artefacts:</u> To be decided.

## 10. Impact Analysis

Change proposals are evaluated, the impact is determined and the proper actions are defined and planned.

Input artefacts: To be decided.

Output artefacts: To be decided.

## 11. Risk Management

To be decided.

In the next paragraph these activities that are defined during the Crystal project are described in more detail.

## 3.2 Detailed Activity Description

From the high level overview described in 3.1 we selected 4 activities, in this section 3.2 these activities are investigated in more detail. Following activities were selected:

- Impact Analysis.

- Requirements.

- Components Engineering.

- System Engineering.

## 3.2.1 Activity: Impact Analysis

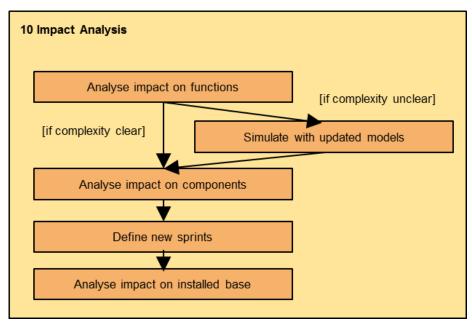

In Figure 3-3, the Impact analysis process is shown. Typically, Impact analysis is started based on a change request, unexpected event or a setback in the intended development approach. The first step is to analyse whether the change has impact on the functions of the system and the corresponding architecture. For this, the current preferred architecture is used as a reference. The impact on function level may be none.

In an advanced approach, the relationships between functions or components are laid down in a design structure matrix which plots functions against functions with an indication of the strength of the interaction between the functions. This can also be done at a component level but will be very elaborate. The design structure matrix can help to quickly oversee impact of changes and is useful for all team members to understand system coherence.

If the complexity and impact of the change is hard to assess and thus unclear, a high level simulation with an updated model can be applied to analyse performance in the new situation and to decide in what way to change functions or preferred architecture. If the complexity is manageable at first analysis, such a simulation is not necessary. The new preferred architecture needs have good traceability to the current version of the requirements.

In a next step, the changes to the preferred architecture and the impact of the change on the various components is analysed based on the component archive of current versions of the components. Needed modifications to the components are described as new sprints.

Finally, the change may also have an impact on the installed base, e.g. if a new failure mechanism is detected. In this step, activities are defined to update the installed base, where necessary.

Figure 3-3: Impact Analysis.

## 3.2.2 Activity: Requirements

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 12 of 75 |

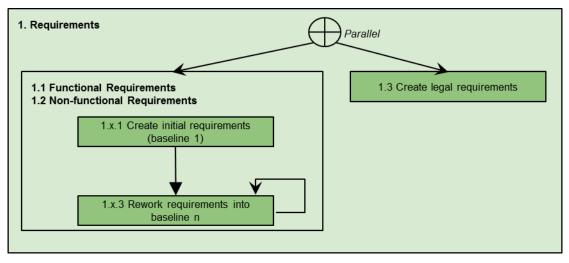

Figure 3-4 shows a detail of the Requirements Activity. The Requirements activity is split into 2 parallel activities: Create Legal Requirements and Create Functional/Non-Functional Requirements. The Legal Requirements activity is mainly involved with research into applicable regulations. The Functional/Non-Functional Requirements Activity is a iterative process that involves inputs from customers and market evolutions. As such, they are continuously updated, even during development of the product.

Figure 3-4: Requirements Process Activities.

## 3.2.3 Activity: Components Engineering

Figure 3-5 shows some details of step 5, i.e., it describes how components are created. The product is divided into constituent components, each with their own requirements. The development process is focused on developing these individual components. Requirements for these components are continuously updated (Backlog refinement), while in parallel, requirements for complete components are being developed (Sprint).

Figure 3-5: Components Engineering Process Activities.

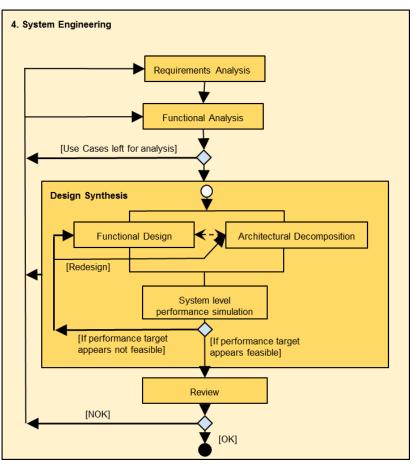

## 3.2.4 Activity: System Engineering

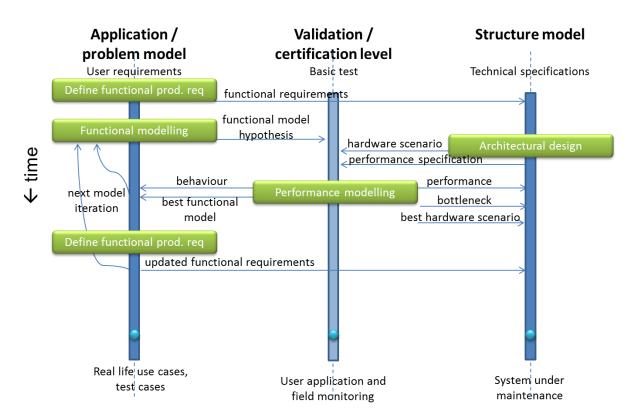

Figure 3-6 gives an overview of the process flow & iterations for the System Engineering. The goal of this activity is to define the executable system architecture.

Figure 3-6: System Engineering.

Table 3-1 show an overview of all process steps for the System Engineering Activity and the according input and output.

| Activity                 | Input                    | Output                                                 | Tool Requirements                                                                            |

|--------------------------|--------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Requirements<br>Analysis | Stakeholder Requirements | System Requirements<br>System Use Cases                | Requirement<br>Management                                                                    |

|                          |                          | System Requirements to<br>Stakeholder Requirements     | Creating Requirements baselines                                                              |

|                          | traceability             | Use Case Modeling                                      |                                                                                              |

|                          |                          | System Use Case to System<br>Requirements traceability | Traceability between<br>Use Cases, System<br>Requirements and<br>Stakeholder<br>Requirements |

|                          |                          |                                                        | Document Generation                                                                          |

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 15 of 75 |

| Activity                  | Input                                    | Output                                                                 | Tool Requirements                                                           |

|---------------------------|------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Functional<br>Analysis    | System Use Cases                         | Top Level Executable<br>Functional Model.                              | Architectural modeling (functional)                                         |

|                           |                                          |                                                                        | Architectural simulation<br>(functional, discrete as<br>well as continuous) |

|                           |                                          |                                                                        | Traceability between<br>model artefacts to<br>System use Cases              |

|                           |                                          |                                                                        | Model Formal<br>Verification                                                |

|                           |                                          |                                                                        | Model Baselining                                                            |

|                           |                                          |                                                                        | Document Generation                                                         |

|                           |                                          |                                                                        | Model reuse                                                                 |

|                           |                                          |                                                                        | Model Consistency<br>Checking                                               |

| Design                    | System Requirements                      | Executable System                                                      | Architectural modeling                                                      |

| Synthesis                 | System Use Cases                         | Architecture:                                                          | Architectural simulation                                                    |

|                           | Top Level Executable<br>Functional Model | System Use Cases                                                       | (discrete as well as continuous)                                            |

|                           | Functional Model                         | Architectural Decomposition                                            | Traceability between                                                        |

|                           |                                          | <ul><li>Component Descriptions</li><li>Executable Functional</li></ul> | model artefacts and to<br>Requirements                                      |

|                           |                                          | Models<br>Architecture to System                                       | Performance Modeling and Simulation                                         |

|                           |                                          | Requirements traceability                                              | Model Formal<br>Verification                                                |

|                           |                                          |                                                                        | Architectural Base lining                                                   |

|                           |                                          |                                                                        | Document Generation                                                         |

|                           |                                          |                                                                        | Model and component reuse                                                   |

|                           |                                          |                                                                        | Model Consistency<br>Checking                                               |

| Functional<br>Design      | System Use Cases                         | Decomposed Executable<br>Functional Model                              | Model and component reuse                                                   |

|                           |                                          |                                                                        | Model Consistency<br>Checking                                               |

| Architectural             | System Requirements                      | Architectural Decomposition                                            | Subsystem                                                                   |

| Decomposition             | System Use Cases                         | Component Descriptions                                                 | Requirements<br>engineering                                                 |

|                           |                                          |                                                                        | Model and component reuse                                                   |

|                           |                                          |                                                                        | Model Consistency<br>Checking                                               |

| System Level              | System Requirements                      | Executable Performance Model                                           | Model Consistency                                                           |

| Performance<br>Simulation | System Use Cases                         | Trade off analysis report                                              | Checking                                                                    |

| Simulation                | Executable System<br>Architecture        | Performance Analysis Report                                            |                                                                             |

| Activity | Input                                               | Output                                | Tool Requirements                        |

|----------|-----------------------------------------------------|---------------------------------------|------------------------------------------|

| Review   | System Requirements                                 | Review comments                       | Review Workflow                          |

|          | Executable SystemReview decisionsArchitecture:      | specification<br>Review commenting on |                                          |

|          | System Use Cases                                    |                                       | Requirements and<br>Architecture         |

|          | Architectural     Decomposition                     |                                       | Traceability with specified Architecture |

|          | Component     Descriptions                          |                                       | Baseline                                 |

|          | Executable Functional<br>Models                     |                                       |                                          |

|          | Executable     Performance Model                    |                                       |                                          |

|          | Architecture to System<br>Requirements traceability |                                       |                                          |

Table 3-1: Input and output of the System Engineering Activity.

## 3.3 Conclusion

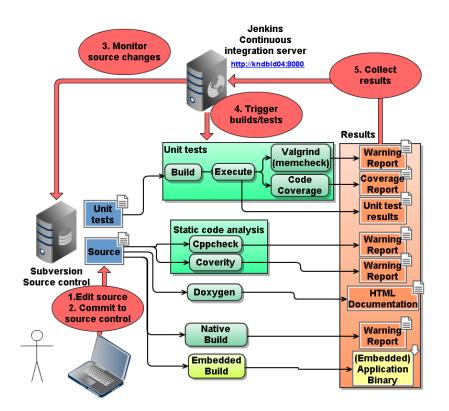

Based on the Barco Roadmap (section 4.0) three implementation tracks were selected to introduce new engineering methods, tools and methodologies for a more software centric and modular approach to the:

- Track 1: New SW design process.

- Track 2: New Hybrid SW Display Platform (F100) design process.

- Track 3: Flexible SW Centric Design Process.

All details about the 3 implementation tracks and their link to the Barco roadmap are described in section 4.

# 4 Identification of Engineering Methods

Section 4 gives a detailed overview of all identified Engineering Methods that contribute to the transformation towards the desired design process for the Barco Use Case.

Please note that not all identified Engineering Methods will be developed in detail in the scope of the project.

Our activities are focusing on those Engineering Methods that are affected by the integration of a new tool, those that provide some interoperability requirements, as well as those contributing to the envisioned desired engineering processes supporting a component-oriented & modular design approach and a software centric display platform.

Section 4.0 is giving more background information for the selected engineering methods and methodologies in CRYSTAL and how these are directly linked to the roadmap of the Barco product platforms and the design processes for 3 new platforms. For each new product platform we installed an implementation track to change the design process by introducing, implementing and evaluating new engineering methods, tools and methodologies,

More details about all Tracks and according engineering methods are described in the following sections 4.1, 4.2 and 4.3.

Section 4.4 is giving an overview of the identified Technical Core Requirements as input to the WP6 activities.

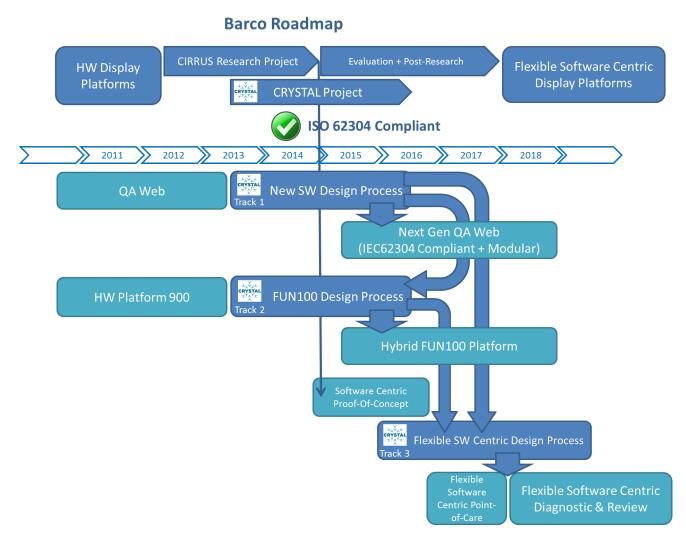

## 4.0 Barco Roadmap and the selected CRYSTAL activities

## Barco Roadmap

The Barco roadmap is to move from custom hardware centric display platforms to flexible software centric display platform using commercial-off-the-Shelf (COTS) components in a fully IEC 62304 compliant design environment is directly linked with the Barco goals and Use Case Description in CYSTAL.

To support this transformation Barco is participating to the CIRRUS and CRYSTAL projects. With the **CIRRUS project** Barco started the research work towards software centric based display platform for diagnostic and clinical review applications, these activities are part of the CIRRUS project, as approved by the Flemish Public Authority IWT (CIRRUS project IWT 120494) and running from 01/07/2012 till 31/12/2014 on national level. The research activities will result in a **first proof-of-concept display platform for diagnostic and review** applications based on software components using COTS hardware. After this first working prototype will be available, a significant amount of **evaluation and post research activities** will be needed before the results of the project can be commercialized. Development effort will be needed on the key components, the integration electronics and mechanics and the EMC validation of the display system. Furthermore extensive validation testing, several pilot series and regulatory approvals will need to be handled as well before commercialization can start of the software centric platform.

As planned on the Barco Roadmap a **first platform using software components running on COTS hardware is planned for the Point-of-care market**. The point-of-care market is a relatively new market for Barco. Initially these products were focused on patient services with a low complexity level, the future trend

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 18 of 75 |

however is to offer services for all stakeholders in the patient care chain (patient, nurses, doctors) at a higher complexity level resulting in the need for smarter products.

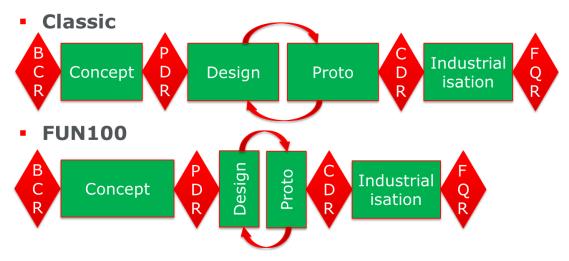

New engineering methods are first implemented in a pure software design process, this is directly linked to the development of our **next gen QA Web software technologies**, these are quality assurance software services bundled with Barco Displays, this is the first implementation track for the Barco CRYSTAL activities: **Track 1: New Software Design Process**. This track will give further input to start and optimize the design processes for the first hybrid software display platform and the software centric COTS display platforms.

The **FUN100** is the new more software oriented platform using one hybrid software source base. The design process for this new product platform is the second implementation track for out CRYSTAL activities: **Track 2: Design Process for FUN100 Platform**. The results of this track will also be used to start en optimize the design process for the software centric COTS display platforms.

The resulting tools and methodologies used in the new software design process and hybrid software FUN100 process will form the first solid base for **Track 3: The Design process for the flexible software centric display platform**. Barco is collaborating with IBM, TNO and TUe to investigate and evaluate new functional modeling and performance simulation techniques to support the hardware selection and design techniques for the software centric display platform are investigated.

Figure 4-1 below depicts the Barco roadmap and the link between the planned CRYSTAL activities to change the Barco design processes for the new product platforms.

Figure 4-1: Link between Barco roadmap and selected CRYSTAL activities.

## Track 1: New Software Design Process

With the introduction of Picture archiving and communication system (PACS) came the need for consistent calibration and quality control for medical displays. Medical QA guidelines like AAPM TG18 and DIN6868-57 were established to quantify and control the quality of medical displays.

The Barco QAWeb service is an all-inclusive secured system is your guarantee for consistent image quality and uptime of all PACS display systems throughout the facility. The system is compatible with Barco diagnostic and clinical displays in addition to non-Barco displays.

The Barco Softcopy QA tools are partly bundled with the display and graphic boards: they allow calibration and control of the graphic board and display so the systems are compliant to DICOM GSDF.

In the context of CRYSTAL Barco started to install a new software design process to ensure the fully IEC 62304 compliancy of the next gen QA Web platform. For this new platform we also want to install a component oriented process, the first concepts have been defined; the more detailed modular design steps will be further worked out in next years of the CRYSTAL project.

More details on the progress of the new software design process are described in section 4.0 of this document.

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 20 of 75 |

## Track 2: Design Process for FUN100 Platform

For the diagnostic and clinical review applications the **Platform 900** is the hardware based product platform of the current display portfolio for these markets.

A first step towards a more flexible and software oriented approach has been taken with the start of the design process for the FUN100 platform.

The FUN100 platform is a hybrid hardware and software platform designed to drive and control medical displays supporting a component-oriented & modular design approach. The FUN100 Platform defines a family of image processing platforms using one software source base which includes both embedded software and VHDL. The same source based is built into multiple deliverables / install packages which typical depend on the interface board and/or the medical displays it is intended for.

In the context of CRYSTAL Barco worked on the following activities:

- A new methodology for the FUN100 architecture supporting a modular approach.

- Test framework for FUN100 (IEC 62304 compliant) by implementing the new engineering methods Component Integration Testing and Software Unit Testing.

More details on the design process for the Hybrid Modular FUN100 platform are described in section 5.4 of this document.

## Track 3: Design process for the Flexible Software Centric Display platform

The tools, methodologies and the according engineering methods as implemented in Track 1 and 2 will form the base of the planned CRYSTAL activities of Track 3, the new design process for the flexible software centric display platform.

To optimize the hardware selection and the modular software design approach for this first software centric point of care medical display platform Barco started collaborating with the CRYSTAL partners IBM, TNO and TUe to investigate and evaluate engineering methods that are not part of the key expertise of Barco.

Together with the research partner TNO and tool partner IBM we are investigating functional modelling, performance simulation and the combination of these 2 engineering methods, these will assist Barco in the support change impact analysis, architectural trade-off analysis and hardware mapping.

The objective of TUe is to predict execution performance of a processing pipeline (gStreamer) more accurately, as part of the intended workflow.

IBM is providing the necessary tool support for these new modeling and simulation techniques.

A pilot project was started at Barco Healthcare with PTC Integrity, other Barco divisions e.g. Barco avionics are using IBM Doors a requirement tool.

As mentioned in the implementation activities of Track 6.1 we noticed that requirements in Integrity are highlevel and broad, as part of CRYSTAL we will investigate and evaluate the new IBM tools for the design process on the development side.

More details on the new Functional Modeling & Performance Simulation Framework are described in section 4.3 of this document.

### **Overview of the Engineering Methods**

Table 4-1 provides an overview of all engineering methods identified at M12 and their according status. Please note that future planned activities are without engineering method ID and some are not yet assigned to an implementation track.

| Track   | EM ID     | EM Description                             | Status                     |

|---------|-----------|--------------------------------------------|----------------------------|

| Track 1 | UC_405_1  | Requirements Gathering                     | First implementation phase |

|         | UC_405_2  | Requirements Traceability                  | First implementation phase |

|         | UC_405_3  | Iterative Development                      | First implementation phase |

|         | UC_405_4  | Process Automation                         | First implementation phase |

|         | UC_405_5  | Key Quality Metrics                        | First implementation phase |

|         | -         | Test Automation                            | Future work                |

| Track 2 | UC_405_6  | Software unit testing                      | Implemented for F100       |

|         | UC_405_7  | Component integration testing              | Implemented for F100       |

|         | UC_405_8  | Architectural Design                       | Implemented for F100       |

|         | UC_405_9  | Software Engineering                       | Implemented for F100       |

|         | -         | Software unit testing                      | Future work for U100       |

|         | -         | Component integration testing              | Future work for U100       |

|         | -         | Architectural Design                       | Future work for U100       |

|         | -         | Software Engineering                       | Future work for U100       |

| Track 3 | UC_405_10 | Functional modeling                        | First implementation phase |

|         | UC_405_11 | Performance modeling                       | First implementation phase |

|         | UC_405_12 | Functional modeling & Performance modeling | First implementation phase |

|         | UC_405_13 | Modular Software Components                | Work in progress           |

| -       | -         | Architectural trade-off analysis           | Future work                |

| -       | -         | Formal Verification                        | Future work                |

| -       | -         | Electronics Engineering                    | Future work                |

| -       | -         | Mechanical Engineering                     | Future work                |

| -       | -         | Automatic Documentation Generation         | Future work                |

| -       | -         | Automatic regulatory compliance testing    | Future work                |

| -       | -         | Not identified Engineering Methods         | Future work                |

Table 4-1: Identified Engineering Methods and Status at t M12.

## 4.1 Track 1: New Software Design Process

## 4.1.1 Introduction

At Barco an initiative was started to research and prototype a tool chain for a new software development process with the following challenges.

## Challenges

- Formalise and streamline requirements gathering.

- Trace requirements throughout the development process.

- Support iterative development.

- Automate processes as much as possible.

- Measure and visualise key quality metrics.

Following Engineering Methods were identified for Track 1:

- UC\_405\_1 Requirements Gathering.

- UC\_405\_2 Requirements Traceability.

- UC\_405\_3 Iterative Development.

- UC\_405\_4 Process Automation.

- UC\_405\_5 Key Quality Metrics.

The sections below describe all selected Track 1 Engineering Methods in more detail.

## 4.1.2 Engineering Method: Requirements Gathering

Up until now requirements were gathered in Microsoft Word and Microsoft Excel documents. Although these documents were based on templates, there was a lot of freedom on how to describe the requirements. Approval of documents was done by emailing the document and pasting an image of a signature into the document. After approval the documents were stored in a central file location.

In order to start agile development, requirements were copied and pasted into the backlog of Atlassian Jira Agile. Changes to requirements involved a labour-intensive manual tracing job.

Although this way of working is fine, it is far from ideal and certainly not easy to fit into IEC 62304 requirements.

It was clear that we needed a more formal way of working and a more 'intelligent' tool than Microsoft Office.

The tool should:

- Be able to import Office documents

- Allow automatic numbering of requirements

- · Integrate seamlessly with our agile and testing tools

- Have an integration interface and a customisable workflow.

## 4.1.3 Engineering Method: Requirements Traceability

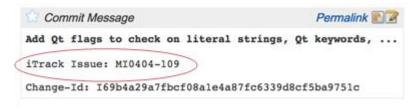

One of the requirements of IEC 62304 is that requirements must be traceable throughout the development process. In short, this means that given a requirement it must be possible to indicate which artefacts have been created to implement and to test that requirement.

More specific this means that it must be possible to trace requirements from the requirement tool to the agile backlog, the user stories, the design documents, the source code, the unit tests, the integration tests and finally to the acceptance tests. Moreover, the results of acceptance tests must be visible on the requirement level. Bugs that are detected (either during development or in the field) should, when applicable, be linked to requirements and acceptance tests.

## 4.1.4 Engineering Method: Iterative Development

The tool chain must support iterative development. This means that requirements do not have to be complete before development can start. However, only approved requirements can be handled in development. Requirements themselves can also evolve over time: they can be fine-tuned, rephrased or even removed.

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 23 of 75 |

Changes to requirements should be easily traceable through the whole development chain, which should help us with impact and risk analysis.

## 4.1.5 Engineering Method: Process Automation

In order for our processes to be repeatable and as error-free as possible and to avoid increased workload and human error, we should strive for as much automation as possible. Results of tests and builds, changes to requirements and lifecycle status of the requirements should be automatically notified to the required tools and stakeholders.

## 4.1.6 Engineering Method: Key Quality Metrics

According to IEC 62304, Medical devices should be under risk management. Risks should be listed and a mitigation plan should be in place. One of the major risks in product development is bugs. Bugs come in many flavours: memory leaks, performance drops, uninitialized parameters, dead- and live-locks, overflow errors, out-of-memory or disk space errors, logic errors, and so on.

Therefore, a number of metrics will be defined that will:

- Measure the product quality.

- Fail a build when certain criteria are not met.

These metrics should be made highly visible through a dashboard and should continuously indicate the health of the product under development.

## 4.2 Track 2: FUN100 Design Process

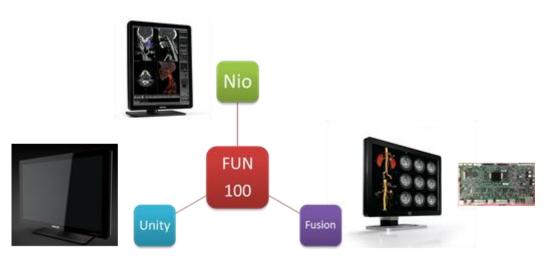

## 4.2.1 Introduction to FUN100

The FUN100 platform is a hardware and software platform designed to drive and control medical displays supporting a component-oriented & modular design approach.

The FUN100 Platform defines a family of image processing platforms. Each platform is targeted for a given range of Healthcare imaging displays. The platforms share a common architecture, but the implementation is scaled to fit the corresponding display range requirements:

- Platform F100 targets our dual-head high-end displays: Fusion.

- Platform U100 targets our new high-end displays: Unity.

- Platform N100 targets our low-cost single-head displays: Nio.

Figure 4-2: Modular FUN100 Platform.

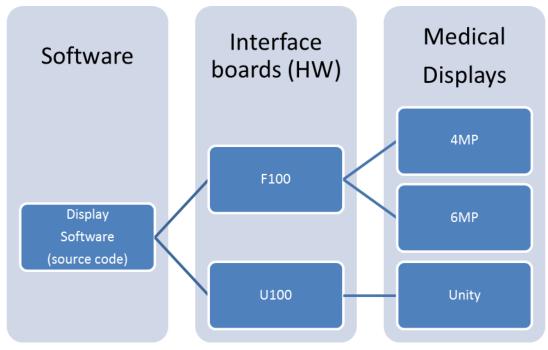

The FUN100 platform is using a common hardware design implemented into different electronic interface boards intended to control medical displays. Currently there are two electronic interface boards defined:

- The F100 interface board, designed for the Fusion type displays.

- The U100 interface board, designed for the Unity type displays.

The FUN100 platform is using one Hybrid software source base which includes both embedded software and VHDL. The same source based is built into multiple deliverables / install packages which typical depend on the interface board and/or the medical displays it is intended for.

Figure 4-3: One Hybrid software base for FUN100.

## Challenges

- Low cost.

- A very tight time to market schedule needs to be met.

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 25 of 75 |

- High data throughput.

- $\circ\;$  Each of the displays pushes the actual data throughput to the limit of the platform.

- Biggest data throughput is required on the U100 platform.

- We have to comply with the new standard regarding software development: IEC-62304.

- IEC-62304 compliant Test Framework.

- Hybrid SW development.

- Modular HW architecture design

## **Identified Engineering Methods for Track 2**

Following Engineering Methods were identified for Track 2:

- UC\_405\_6 Software Unit Testing for FUN100.

- UC\_405\_7 Component Testing for FUN100.

- UC\_405\_8– Architectural Design for FUN100.

- UC\_405\_9 Software Engineering for FUN100.

We sections below describe all these selected Track 2 Engineering Methods in more detail.

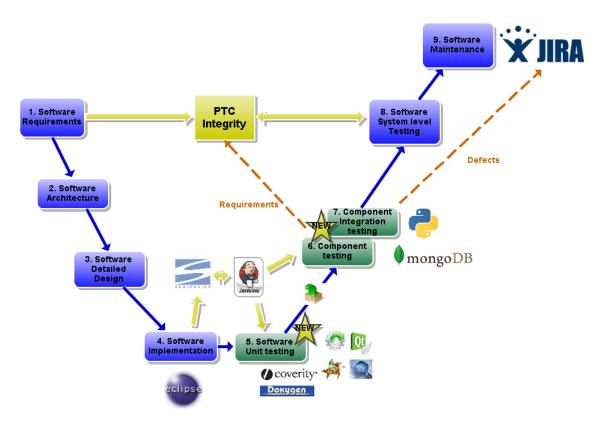

## 4.2.2 IEC-62304 compliant Test Framework for FUN100

## Rationale

- 1. Required for medical applications: IEC-63204.

- 2. Growing need due to increase of complexity.

- 3. To find bugs earlier, shorter time to market.

### Goal

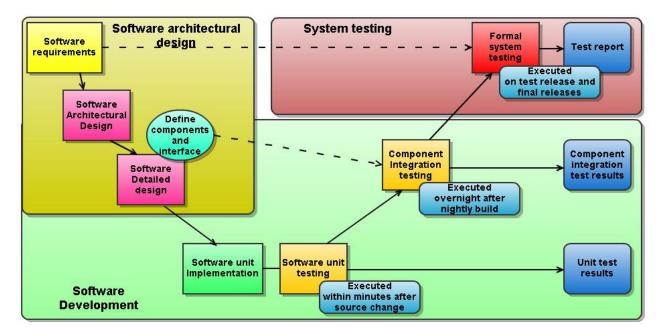

In the FUN100 Testing Framework software testing will be tackled on three levels:

- Unit testing performed by software development team.

- Component integration testing performed by software development team.

- System testing by the validation team.

### **Desired Test Framework**

Figure 4-4 below is giving an overview of the desired test for the FUN100 platform, compliant with IEC-62304.

Figure 4-4: Desired FUN100 Test Framework.

## Challenge

The most challenging of these three is the component integration testing which exists at a level between unit testing and system validation but has certain overlap with both areas. Where unit testing is typically white-box and system testing is typically black box the component integration is something which lives between both.

### Requirements related to IEC62304:

- Trace requirements into architectural design and component test.

- Testing of SOUP (Software Of Unknown Provenance).

- Testing at unit and component level.

# Requirements related to obtain a shorter development cycle from software implementation to software release:

- Automation of testing

- Earlier detection of issues:

- Do earlier testing by having unit and component level testing.

- $\circ$  Monitoring system parameters to be able to trace when a system parameter started deviating.

- Continuous integration: Make implemented code immediately available and have it tested as soon as possible

## Requirements for the (component) testing framework

- The framework should be (at least partially) reusable for other means (system validation).

- Testing should be as automated as possible reducing regression/validation testing cycle.

- It should allow testing interfaces of components.

- As everything it should be lightweight, easy to master, extensible with a minimum of overhead.

- All testing should be integrated, and the execution of tests (and thus also the gathering of reports) should be triggered from a single place.

- Scalability: It should be possible to run multiple instances in parallel (e.g. multiple test stations).

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 27 of 75 |

• It should also be possible to run individual tests/test cases.

We started implementing 2 engineering methods to implement the new Test Framework:

- Software Unit Testing for FUN100

- Component Testing for FUN100

## 4.2.3 Engineering Method: Software Unit Testing for FUN100

#### Goal

Unit testing is done at source code level. It tests whether the source code is implemented as is expected. Unit testing is the type of testing that is closes to the actual implementation (coding) of the software and has therefore the potential to do the most detailed form of testing.

#### Characteristics

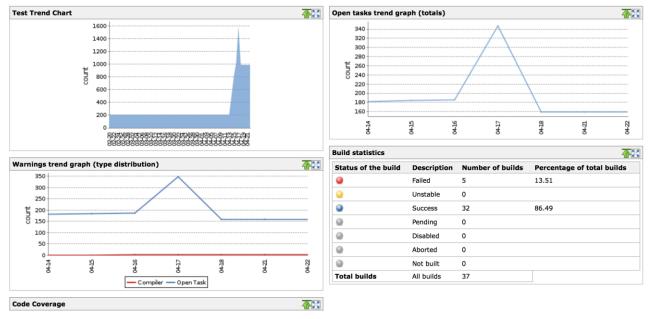

- Automated: Automatically ran by Jenkins after a source change.

- Fast response: Executed within minutes after a change.

- Non-embedded: Runs on the build host or developers workstation, using hardware abstraction and mocks to simulate the hardware and other components.

- Test a class/source of an embedded application.

## 4.2.4 Engineering Method: Component Testing for FUN100

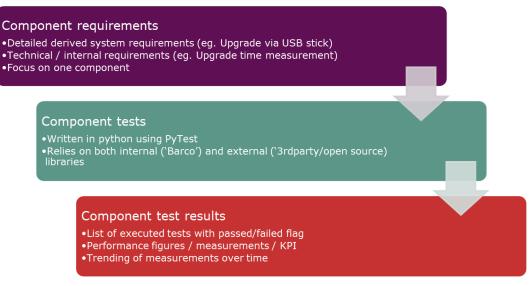

#### Goal

The primary goal of the component testing is to test the individual software components of the software and the interfaces between it.

The component tests will test the FUN100 platform software which is running on actual hardware. Since the support has to support multiple interface boards and displays the component tests will need to be executed against multiple hardware configurations.

The component tests serve three purposes:

- 1. Maintaining stability during software development: For this the component tests are run automatically every night on several units upgraded to the latest software. The goal here is to detect defects as soon as possible after they were introduced due to software development

- 2. Serve as a stage gate towards the system testing. Component tests are to be run on every test release before these are delivered to the system test team. This is done on a representative hardware configuration set.

- 3. Monitor important system parameters during software development. The component tests keep track of important system parameters across multiple tests runs.

### Characteristics

- Automated: Automatically ran by Jenkins every night.

- Medium response: Executed within hours after a change.

- Embedded: Run on the actual hardware.

- Tests at component level:

- Embedded applications, FPGA, Linux kernel.

- Interaction between components.

- Grouped per component, test can be rerun for a single component.

- Configurable:

- Fast / Slow tests.

- o Remote / Local tests.

- o Different types of hardware.

#### Workflow

Workflow Component Testing workflow for FUN100.

The SEE for this new Test Framework is shown in section 5.2.1, the first implementation result can be found in section 6.2 and 6.2.2.

## 4.2.5 Engineering Method: Architectural Design for FUN100

This section describes in detail the new methodology for the FUN100 architecture supporting a hybrid software base.

### Rationale (Pre-CRYSTAL status)

At the end of the development of platform 900, we found that the complexity had increased to a level that made it extremely difficult to maintain. Each problem, in production or in the field, resulted in a complicated investigation during which engineers had to step through the complete design to find the location of the problem. The solution usually resulted in a complicated series of changes, which impacted the total design. In the end, much of the testing and validation had to be redone, because no-one was sure which parts were affected. This was an expensive situation.

The complexity was created by adding functionality on previous platforms without sufficiently questioning the architecture. That resulted in a design which could not be broken down in different parts to isolate problems. Also dedicated software was made for each hardware implementation, so a rather large matrix of versions began to exist.

Both in hardware and software solutions were added which did not really integrate in the architecture, with a lot of overhead as a result. The advantage of this way of working was that a solution was ready for the market in a relatively short time. However, both the direct cost and the maintenance cost increased.

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 29 of 75 |

There was clearly a need to take the next step: the development of a derived platform, which would basically support the same functionality. But this time with a completely new architecture based on modularity and reuse. It was also the intention that next generation displays could be derived without a lot of effort, and integrating new functionality would be straightforward.

## FUN100 Concept

The concept for the new platform was to have no more hardware on the board than strictly needed for the product. This means that more hardware versions would be needed, but each at an optimized size and cost.

The drawback would be that this means more development time. However the modular design meant that a new hardware version was easily derived, and the software was almost instantly ready due to the parametered modules.

## Strong focus on Testability

For this new platform the decision was taken to implement automatic unit testing and component testing, so that debugging in a later stage could be done more efficiently. Tests are available in software, but once the hardware was available, the same tests were also run in the hardware environment. This creates the possibility to isolate bug solving to the module level, and due to the automatic testing, any change is immediately evaluated and ready to be released.

## Conclusion

The SEE for this new FUN Architecture methodology is shown in section 5.2.2, the first implementation result can be found in section 6.2.3.

## 4.2.6 Engineering Method: Software Engineering for FUN100

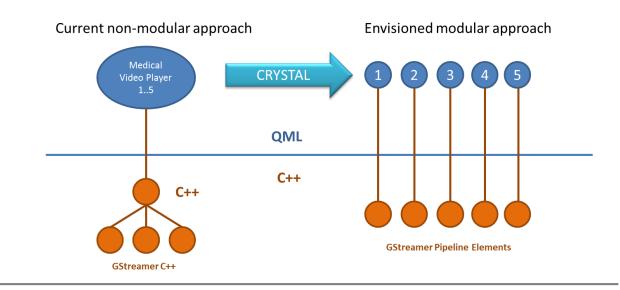

This section describes in detail the new methodologies and techniques that were started in Barco to implement a modular approach for the software engineering process for the FUN100.

## Portability

#### A model driven design approach

The rationale of a model driven design approach is the reuse of IP (Image Processing) in all healthcare displays, regardless of the megapixel count, FPGA device family and other product specific parameters. At the moment of this writing Barco Healthcare has implemented many real time image processing applications often with low latency requirements, although the investigated high level platform approach is not restricted to this real time aspect and could, for instance, eventually be applied for video file format conversions in storage devices or for pseudo real time quality of service analysis.

Applications include any adaptations or transforms required for any type of video sources to any information carrier as well as conversions required by the destination, for instance the diagnostic display. Examples of video sources include digital endoscopy cameras, graphical cards, streaming video over a networks, video or image file formats. Typical examples of adaptations for such a sources include (de)interlacing, resizing, (de)compression, Chroma up sampling, noise reduction, motion compensation, edge enhancement, sharpening, histogram equalization, automatic contrast control, ...

In diagnostic displays typical examples are colour space conversions, (de)gammatization, sRGB colour profiles, picture uniformity correction, x-talk compensation, frame rate conversion, temporal display response optimization, grey tracking (according to DICOM), perceptual matching, graphical overlay, colour gamut mapping, electro-optical transfer functions, dithering... The information carrier can be any type of memory or storage device such as DDR memory chips or a flash hard disk, any (local) standard bus such as PCIe, a global or local network. Eventually an image processing application prepares and optimizes the video data

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 30 of 75 |

for a specific destination or sink, which can be a display device, a new IP video stream on a network, a new file...

Barco currently has an elaborated set of image processing modules. Many of the image processing applications such as 3D colour profiles or dithering have been developed for different implementations in different hardware and/or software environments. In order to reuse the existing IP within all implementations based on the FUN platform, the Fusion,Unity and Nio displays, the processing chain needs to be re-shaped according to a common model, with elements implementing a common interface. High level source code should enable the reuse of existing IP without considerable modifications to the source code. The embedded software which communicates with the IP blocks therefore will "see" a common interface for all displays.

#### Interoperability - need for standard bus interface

The second reason to model the processing chain is the increasing need for interoperability between various product families and thus the increasing need for adherence to standards. A standard bus interface protocol must be used which can be implemented in both Xilinx and Altera devices and communicate with the corresponding "native" IP libraries, such as memory controllers. Therefore the flow control bus protocol must unify the streaming AXI interfaces, common in Xilinx devices, and the streaming Avalon busses (including the burst mode transfers).

The healthcare displays products evolve from simple boxes towards more complex distributed and integrated systems, with an increasing use of off-the-shelf components, usually in software, licensed with commercial licenses or as open source software. The technological convergence and increasing price pressure drives the re-use of components across multiple products, even if they are deployed in different markets with different end-user requirements. This enforces the R&D departments to design their components to be more flexible and generic.

#### IP Reuse

Barco has multiple proprietary colour processing implementations based on different FPGA families (such as Altera Stratix or Xilinx Virtex) and different CPU based software implementations. The company's subdivision Silex even developed multiple ASIC devices dedicated to colour processing applications, for instance to calibrate the grey tracking of a display (the LUT ASIC). This means many different types of colour processing architectures exist simply because they use different implementation devices. Within the scope of this platform an inventory is created of the existing IP applications. Based on that we can identify what caused the different implementations of the same functionalities to coexist. Identifying the root causes for this coexistence will be a key element to determine the required capabilities of any future high level code to be developed, regardless of the language to be used.

Related to the above study is the identification of the root causes why proprietary applications or processing blocks were developed instead of COTS solutions. If COTS solutions were used, it is equally important to determine what made them "good enough" for a given application. The high level image processing chain should be capable to absorb the above mentioned functionalities, as well as to interface with them by using interfacing methods and architectural description methods to be determined within the current research.

## Scalability

#### Data throughput and latency requirements

When one wants to process large amounts of data efficiently (for instance to handle 12 megapixels in real time with high accuracy of about 64 bit per pixel) and with low latency, one needs to take into account the locality of the images on the host device. In a high demanding application a lot of time is wasted in copying data around. The latency and throughput of the memory transfers become the bottleneck of the application.

To make things even worse the optimal architecture for high end applications with a high throughput demand not only depends on its host device but also for instance on the type of connected DDR devices (DDR2,

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 31 of 75 |

DDR3, RLDRAM, QDRAM...) as many image processing applications such as resizing require storing the images in some sort of frame memory.

An abstraction layer, build in to the bus communication protocol of the image processing, should accommodate for a generic external image frame store configuration, depending on the latency requirements. Different approaches exist to interconnect the image processing application with the dedicated memory devices. So far, often the image processing application had to be adapted for a specific memory controller type, which makes the usage of a COTS solution (for instance a memory controller offered by the FPGA vendor) difficult.

The current research attempts to resolve this type of issues by describing the image processing application in a generic way that includes a more abstract definition of for instance the memory transfer operations. A simple high level abstract description of the system or the host device environment would enable the reuse of a high level described image processing feature without the usual considerable modifications to the source code.

The framework must support measuring, configuring and controlling the data throughput typically expressed as image frame-rate and at the same time it must support measuring, configuring and controlling the timing behaviour or latency of individual elements and the complete pipeline.

#### Parallelisms within the IP chain

The architecture must also support the concepts of parallel and serial processing. Further investigation must define how this can be modelled and to what extend the processing can be predicted and what accuracy can be achieved.

An important aspect is the reuse of embedded software drivers for multiple architectures. The software should not "know" the difference between for example a single processing engine running at 800 MHz or four combined processing engines parallelized and running at 200 MHz. The FPGA architecture, and thus all image processing blocks included, must be foreseen for parallel architectures. The goal of the current coding methodology for this platform is to achieve the ultimate scalable solution. In short term, for instance, the IP framework should offer a fairly optimized solution for 3 megapixel displays (Nio), 6 megapixels (Fusion) and 12 megapixels (Unity).

### Model the interconnections between IP blocks

A standard image processing block interconnection method has to be developed which has the flexibility to adapt to the above mentioned combination of bottom-up capabilities propagation trough the hierarchy and top-down generic configuration of the global application.

Ideally 1 virtual interconnection between any 2 image processing blocks within the chain should be sufficient. Such a "bus" should be a subset of a framework to connect the image processing application with other functionalities, for instance PCIe controller or a LAN interface. Preferably the application's boundaries should interface with other (COTS) blocks in the system by using a COTS protocol such as AXI4 or Streaming Avalon or the high level framework should provide functions to adapt its native interfacing format to any of such a required standard interfaces. Such a conversion feature should also be developed for the internal block interconnections within the application for debugging and validation purposes as this allows the usage of COTS validation tools to be used. We must further investigate how it needs to be modelled, and what is needed to reach the predictability and QoS.

#### Runtime support for quality of service

A quality of service analyser should be included based on the current environment, input and output format, viewing conditions, quality metrics specific for the application and other aspects, for instance to guarantee DICOM compliancy.

In the example of a colour transform a QoS analyser could report the J-index variation per quantizing interval based on:

• The current image content (multiple aspects).

| Version | Confidentiality Level | Date       | Page     |

|---------|-----------------------|------------|----------|

| V01.00  | R                     | 2014-04-30 | 32 of 75 |

- The display type (colour gamut, resolution, size,...).

- The QoS could produce a warning message when for instance the image is not guaranteed to be diagnostically lossless in a critical healthcare application (for instance caused by a too low resolution display). It should compare the currently provided quality to a pre-defined critical specification.

In the example of an electro-optical transfer compensation block for a display a QoS analyser could report the percentage of image detail loss based on:

- The optical electric transfer function provided by the current source format such as sRGB, DICOM, Rec.709, Adobe RGB, ...

- Ambient light conditions

- Defined quality metrics for the application (for instance DICOM–based just noticeable difference curves as used in healthcare)

- Here again the QoS analyser could trigger a warning message when some quantizing levels become invisible on the display system.

## Highly configurable

#### Risks and challenges related to highly configurable coding techniques

The intended methodology which will be used to synthesize the IP framework in FPGA raises a couple of questions and challenges:

- Feasibility of the current compilers XST, Quartus and ModelSim: how well do these tools handle highly generic code? How "deep" can generics be propagated through VHDL 2008 designs?

- Development of a library for all required mathematical functions such as Sinc, Fourier transform, logarithms, matrix inversions...: how fast can the above tools compile these functions? What is the optimal real tolerance? Can the tolerance aspect be made compatible with OpenCL?

- Image processing chain modelling to optimize the performance <> resources <> quality <> Latency trade off. Resource balancing (DSP, logic, RAM, IO bandwidth...) should also be configurable.

- How to make a module adapt to its environment without making the code too complex (port standards used...). Increasing the generic level should even increase readability compared to base code.

- From a certain integration level, we need to standardize the interfaces: what to use? A dedicated video bus, Axi4, Streaming Avalon, G-streamer like interface...

- Integrate the embedded software model to obtain a diamond model for the image processing chain. Which libraries are optimal to integrate C-based software and VHDL-based hardware? Do we need to write new libraries for this? Do we need system C to bridge?

- Reuse the same code in multiple products based on the FUN –Platform. Do we need any device specific libraries for optimal implementation towards the target FPGA which is different for the Fusion, the Nio and the Unity?

- A Wrapper file must be created per project to align integration methodology for all projects derived from this platform. How can these different configurations be integrated in a regression testing platform? Is synthesizing an array of all known IP chain instances feasible with the current synthesis/simulation tools?

- How to apply the concept of model-driver design for system validation for the different use cases based on the diamond model (embedded software + FPGA hardware)? Can hardware always be modelled bit-accurately in software with standard libraries?

- Resource optimization (by combining multiple image processing aspects such as colour space conversions and electro-optical transforms) when integrated in the product.

#### High level functionalities

The model of the image processing platform must support the following high level functionalities: quality parameters are often market specific as the requirements for the same application can be very different.

Consider for instance temporal response optimization algorithms: they can be optimized differently for different types of moving images. Algorithms which introduce so called overshoot artefacts can be perfectly acceptable in broadcasting applications as they should not be visible on bandwidth limited video sources, but they can be unacceptable for diagnostic applications as they could lead to false diagnosis.

For example, grey level tracking has to be very accurate in many healthcare applications to ensure all quantizing steps are almost equally visible according to the DICOM standard, while in a digital cinema projector the whole colour gamut is of equal importance according to the DCI specifications. This means the configuration of a high level image processing application should depend on the global application and even the market it is used in. In some markets artefacts should always be minimized as much as possible, while other markets, such as most applications within the healthcare market, prefer to have predictable artefacts even if this would reduce the overall image quality.

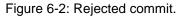

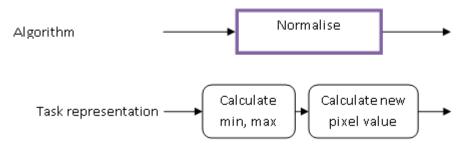

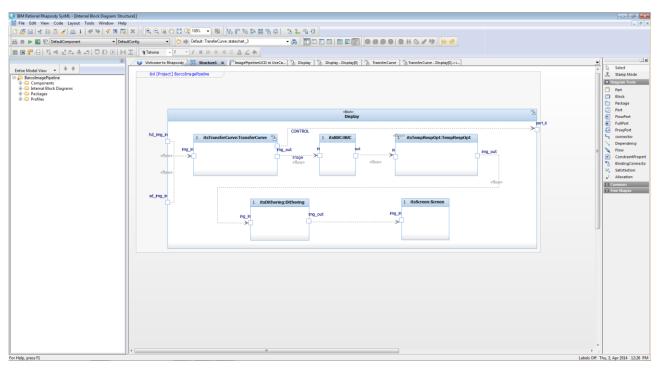

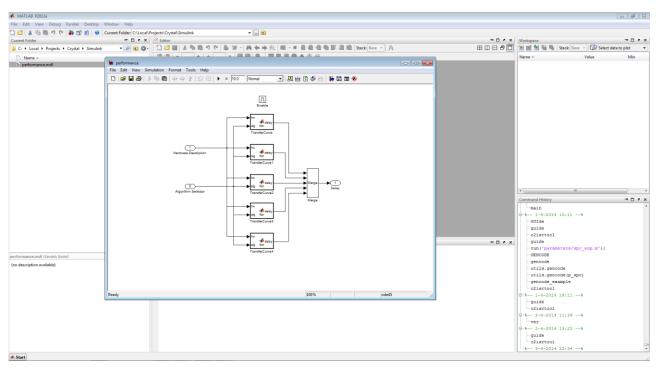

In addition to image quality, another important aspect is low latency while having a high throughput. Acceptable latencies differ from the application, and even the type of operation. Some health care applications, such as endoscopic surgery, have very strict low latency requirements.